基于FPGA原型的SoC开发与软件开发设计流程

随着集成电路技术的飞速发展,片上系统(System-on-a-Chip, SoC)的设计日趋复杂,集成度不断提高。在此背景下,基于现场可编程门阵列(Field-Programmable Gate Array, FPGA)的原型设计方法,已成为SoC开发流程中验证硬件架构、加速软件开发的不可或缺的关键环节。本文将系统阐述基于FPGA原型的SoC开发流程,以及与之紧密相关的软件开发与协同设计。

一、FPGA原型在SoC开发中的角色与优势

FPGA原型设计,是指利用大规模、高性能的FPGA平台,将目标SoC的硬件设计(通常是寄存器传输级,RTL代码)进行综合、映射与实现,构建一个在功能、时序和接口上尽可能接近最终芯片的物理可运行系统。其核心价值在于:

- 早期硬件验证:在昂贵的流片(Tape-out)之前,提供一个真实、可调试的硬件平台,用于验证复杂逻辑功能、总线协议、时钟与复位设计等,极大降低流片风险。

- 并行软件开发:软件团队可以在真实的硬件原型上,并行进行操作系统移植、驱动程序开发、应用程序调试与性能优化,将软件开发周期提前数月,实现“软硬件协同开发”。

- 系统级性能评估:原型系统可以运行真实的软件负载,为评估系统整体性能、功耗热点、带宽瓶颈提供实际数据,指导架构优化。

二、基于FPGA原型的SoC开发主要流程

该流程是一个迭代与协同的过程,主要包括以下阶段:

- 架构设计与RTL实现:根据系统需求定义SoC架构,包括处理器核心、总线互连、存储器控制器、外设IP等,并完成RTL代码编写。

- FPGA原型平台选型与准备:选择容量、性能、接口资源匹配的FPGA开发板或多FPGA分割平台。准备必要的原型辅助组件,如时钟管理、外部存储器接口、调试接口(如JTAG、串口)等。

- 设计适配与综合:将目标SoC的RTL设计进行针对FPGA的适配。这通常包括:

- IP替换与包装:将部分工艺相关的硬核IP(如PLL、高速接口)替换为FPGA厂商提供的等效IP核。

- 时钟与复位结构转换:将ASIC中的复杂时钟树简化为FPGA支持的有限全局时钟网络。

- 存储器实例化:将片上SRAM/ROM用FPGA的块RAM(BRAM)实现。

- 逻辑综合与布局布线:使用FPGA工具链进行综合、映射、布局布线,生成可下载的比特流文件。

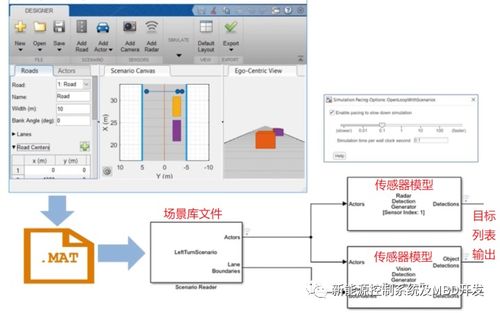

- 系统集成与调试:将比特流加载到FPGA原型平台,连接必要的外设。利用内嵌逻辑分析仪(如Xilinx的ILA、Intel的SignalTap)或外部测试设备进行硬件调试,确保基本功能正确。

- 性能分析与迭代优化:在原型上运行测试向量,分析时序、资源利用率和功耗,并根据结果返回修改RTL设计或架构。

三、面向FPGA原型的软件开发与设计

FPGA原型为软件开发提供了“左移”(Shift-Left)的宝贵机会。相关的软件开发活动包括:

- 板级支持包(BSP)与固件开发:针对原型平台的特定硬件配置,开发或移植Bootloader、时钟初始化代码、设备驱动程序的底层固件。这需要深入了解FPGA原型中各个IP的地址映射、中断分配等硬件细节。

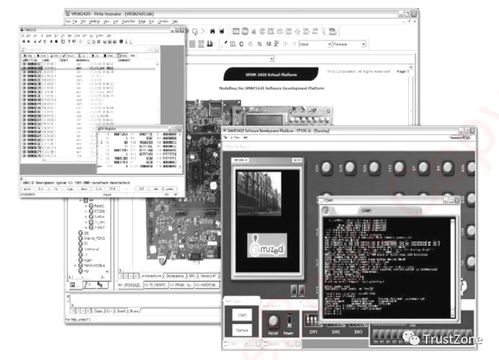

- 操作系统移植与驱动开发:将实时操作系统(如FreeRTOS)或通用操作系统(如Linux)移植到原型平台。为自定义的硬件IP编写内核驱动程序,并验证其功能与稳定性。

- 应用程序开发与系统验证:在原型上运行真实的应用程序或基准测试套件(如Dhrystone, CoreMark),进行功能验证和性能剖析。这能暴露出软硬件交互中的深层次问题。

- 硬件/软件协同调试:利用原型平台实现硬件事件与软件执行的联动调试。例如,通过设置硬件断点触发软件调试器暂停,或通过软件写入特定寄存器来观察硬件信号变化。

四、挑战与最佳实践

基于FPGA的SoC原型开发也面临诸多挑战:

- 性能差异:FPGA的工作频率通常远低于最终ASIC,可能掩盖某些时序问题。

- 资源限制:超大规模的SoC设计可能需要多颗FPGA进行分割,引入分区设计和互连延迟的复杂性。

- 调试能见度:与仿真相比,原型上的内部信号观测相对困难。

应对这些挑战的最佳实践包括:

- 早期规划:在SoC架构设计阶段就考虑原型需求,采用可综合的编码风格和便于分割的模块化设计。

- 采用专业原型平台与工具:使用集成了高速互连、丰富外设和强大调试能力的商用原型系统,以及支持多FPGA分割和协同仿真的工具链。

- 建立高效的软硬件协同流程:定义清晰的硬件抽象层(HAL)和API,确保软件能在不同抽象级别的平台(仿真模型、FPGA原型、最终芯片)上平滑移植和测试。

###

总而言之,基于FPGA的原型设计是现代复杂SoC开发流程中的战略支点。它不仅显著降低了硬件开发风险,更重要的是,它打通了软硬件之间的壁垒,使得软件开发得以与硬件开发深度并行。一个规划良好、执行高效的FPGA原型项目,能够大幅缩短整个SoC产品的上市时间,提升最终产品的质量与竞争力。随着FPGA容量和性能的持续提升,以及相关设计自动化工具的日益成熟,其在SoC开发中的地位将愈发重要。